November 25, 2015, 2:25 am

hi

I'm a vhdl developer and use frequently the quartus compile. This weekend is expired the evaluation licence for the Quartus II (my version is 15.0) and I've supplied the time-limited licence downloaded at the Altera licence page since I've an evaluation board for a Stratix 5.

After the first compilation I've noticed that the result is quite different from the evaluation full licence that the altera FAE has supplied me. So I've request a new evaluation full licence meanwhile the full licence will be provided by the supplier.

The problem is that despite I'm pointing the evaluation licence the quartus is still running as Time-limited.

Where is placed the setup to get back again the full Qurtus performance? It seems is still running as Tiime-limited since the .sof file is named as xxxtime-limited.sof.

Thanks in advance to anybody will solve this issue.

↧

November 25, 2015, 2:48 am

Hi,

I need to interface a image sensor (OnSemi Python300 - 4 LVDS lanes where each lane runs@360 MHz, 720 Mbps).

I'm confused between MAX10 and CYCLONE5 FPGAs for it.

Could anyone suggest me a dev kit for either of these FPGAs where I can directly connect the image sensor PCB? (I think it won't be good to connect it via just about any header pinas LVDS connections need to be matched in length and short. If I'm wrong, please correct me).

Thank you so much !

P.S. - If somebody could also help in choosing between these two FPGAs then that would be great too. I just need to take the image data, store it on a memory/RAM and later send it via some communication method like Ethernet/WiFi. The datarate from the sensor will be high (~700 mbps). Thanks again !

↧

↧

November 25, 2015, 3:19 am

Hi,

If I am in the chip planner or in the RTL viewer and a select a block and then I can go and select Locate-> Resource Property Editor and then the Resource property editor opens.

My questions is: can I open Resource Property Editor in another way - i.e. without looking to locate someting?

What is the point of Resource Property Anyways? I failed to find this in altera documentation I only found this:

http://quartushelp.altera.com/14.0/m...rty_editor.htm

and it doesn't really say a lot to me.

Thank you in advance for your comments.

↧

November 25, 2015, 7:10 am

↧

November 25, 2015, 7:12 am

I am having difficulties getting the MTL Paint Demo to work under Quartus 15.0. When building the BSP, the ALT_ENHANCED_INTERRUPT_API_PRESENT flag is set. I make the appropriate modifications to the MTC_Init and mtc_ISR routines to handle the newer rather than the legacy interrupt interface and I can receive interrupts. I have a problem writing to the LCD, either through the gui_vpg or gui calls. If I choose the gui_vpg option and step through, the call to never returns. It ultimately calls vid_paint_block. It appears that this routine hangs after processing 128 lines when attempting the memcpy near the end of that routine.

Has anyone been able to run this demo in the Eclipse debugger in V15.0? Why would this happen here? It seems that the memory size should be enough.

↧

↧

November 25, 2015, 7:49 am

Hello guys, i have a problem with simulation in altera modelsim about serial input parallel output shifter register

Code:

vhdl code:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity sipo1 is

port (

clk : in STD_LOGIC;

reset: in STD_LOGIC;

D : out unsigned(7 downto 0)

);

end sipo1;

architecture behavioral of sipo1 is

signal temp : unsigned(7 downto 0) := (others => '0');

begin

D <= temp;

process (clk)

begin

if (rising_edge(clk)) then

if (reset = '1') then

temp <= (0 => '1', others => '0');

else

temp(1) <= temp(0);

temp(2) <= temp(1);

temp(3) <= temp(2);

temp(4) <= temp(3);

temp(5) <= temp(4);

temp(6) <= temp(5);

temp(7) <= temp(6);

temp(0) <= temp(7);

end if;

end if;

end process;

end behavioral;

Code:

testbench:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY sipo1_tb IS

END sipo1_tb;

ARCHITECTURE behavioral OF sipo1_tb IS

-- constants

-- signals

SIGNAL clk : STD_LOGIC:= '0';

SIGNAL D : STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL reset : STD_LOGIC:= '0';

constant clk_period : time := 20 ns;

COMPONENT sipo1

PORT (

clk : IN STD_LOGIC;

D : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

reset : IN STD_LOGIC

);

END COMPONENT;

BEGIN

uut : sipo1

PORT MAP (

-- list connections between master ports and signals

clk => clk,

D => D,

reset => reset

);

clk_process : PROCESS

-- variable declarations

BEGIN

-- code that executes only once

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

END PROCESS;

sipo1_1 : PROCESS

-- optional sensitivity list

-- ( )

-- variable declarations

BEGIN

-- code executes for every event on sensitivity list

reset <= '1';

wait for 4 ns;

reset <= '0';

wait for 5 ns;

reset <= '1';

wait for 2 ns;

reset <= '0';

wait;

END PROCESS sipo1_1;

END behavioral;

the error is "PAUSED AT LINE 12", in the next script, I show more detailed error

Code:

# Reading C:/altera/15.0/modelsim_ase/tcl/vsim/pref.tcl

# do sipo1_run_msim_rtl_vhdl.do

# if {[file exists rtl_work]} {

# vdel -lib rtl_work -all

# }

# vlib rtl_work

# vmap work rtl_work

# Model Technology ModelSim PE vmap 10.3d Lib Mapping Utility 2014.10 Oct 7 2014

# vmap -modelsim_quiet work rtl_work

# Copying C:/altera/15.0/modelsim_ase/win32aloem/../modelsim.ini to modelsim.ini

# Modifying modelsim.ini

# ** Warning: Copied C:/altera/15.0/modelsim_ase/win32aloem/../modelsim.ini to modelsim.ini.

# Updated modelsim.ini.

#

# vcom -93 -work work {C:/Users/SAULO/Downloads/PROYECTOS FPGA/Tarea/sipo1/sipo1.vhd}

# Model Technology ModelSim ALTERA vcom 10.3d Compiler 2014.10 Oct 7 2014

# Start time: 10:29:17 on Nov 25,2015

# vcom -reportprogress 300 -93 -work work C:/Users/SAULO/Downloads/PROYECTOS FPGA/Tarea/sipo1/sipo1.vhd

# -- Loading package STANDARD

# -- Loading package TEXTIO

# -- Loading package std_logic_1164

# -- Loading package NUMERIC_STD

# -- Compiling entity sipo1

# -- Compiling architecture behavioral of sipo1

# End time: 10:29:18 on Nov 25,2015, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

#

# vcom -93 -work work {C:/Users/SAULO/Downloads/PROYECTOS FPGA/Tarea/sipo1/simulation/modelsim/sipo1_tb.vhd}

# Model Technology ModelSim ALTERA vcom 10.3d Compiler 2014.10 Oct 7 2014

# Start time: 10:29:18 on Nov 25,2015

# vcom -reportprogress 300 -93 -work work C:/Users/SAULO/Downloads/PROYECTOS FPGA/Tarea/sipo1/simulation/modelsim/sipo1_tb.vhd

# -- Loading package STANDARD

# -- Loading package TEXTIO

# -- Loading package std_logic_1164

# -- Compiling entity sipo1_tb

# -- Compiling architecture behavioral of sipo1_tb

# End time: 10:29:20 on Nov 25,2015, Elapsed time: 0:00:02

# Errors: 0, Warnings: 0

#

# vsim -t 1ps -L altera -L lpm -L sgate -L altera_mf -L altera_lnsim -L cycloneive -L rtl_work -L work -voptargs="+acc" sipo1_tb

# vsim -gui "+altera" -l msim_transcript -do "sipo1_run_msim_rtl_vhdl.do"

# Start time: 10:29:20 on Nov 25,2015

# Loading std.standard

# Loading std.textio(body)

# Loading ieee.std_logic_1164(body)

# Loading work.sipo1_tb(behavioral)

# Loading ieee.numeric_std(body)

# Loading work.sipo1(behavioral)

# ** Failure: (vsim-3807) Types do not match between component and entity for port "D".

# Time: 0 ps Iteration: 0 Instance: /sipo1_tb/uut File: C:/Users/SAULO/Downloads/PROYECTOS FPGA/Tarea/sipo1/sipo1.vhd Line: 9

# Fatal error in file C:/Users/SAULO/Downloads/PROYECTOS FPGA/Tarea/sipo1/sipo1.vhd

# while elaborating region: /sipo1_tb/uut

# Fatal error in file C:/Users/SAULO/Downloads/PROYECTOS FPGA/Tarea/sipo1/simulation/modelsim/sipo1_tb.vhd

# while elaborating region: /sipo1_tb

# Error loading design

# Error: Error loading design

# Pausing macro execution

# MACRO ./sipo1_run_msim_rtl_vhdl.do PAUSED at line 12

any solution? please :(

↧

November 25, 2015, 9:28 am

I have a system, wherein user logic is interfaced to DDR1 SDRAM Controller using native interface in Cyclone 2 device. The project was built in Quartus 11.1 and when we generate the DDR1 IP, either Avalon-MM or Native interface could be generated.

Now, the whole idea is to change the memory module from DDR1 to DDR3 in Cyclone V device. But, when I try to generate the core, native interface is not supported and only Avalon interface is supported. Now I need some sort of code/IP which converts Avalon-MM to Native interface signals?

Can anybody help me regarding this?

↧

November 25, 2015, 9:49 am

Hi folks. I built a simple system using Qsys (packaged with Quartus Prime 15.1) with some onchip memory for cpu instruction and data, plus a separate dual port RAM (data width 32, 1024 bytes, base address 0x1000) for passing data back and forth between FPGA logic and CPU. The other components in the system are a uart, 50MHz clock and System ID component. Using a Terasic Cyclone V FPGA Starter Kit.

I initialize the RAM with a .hex file generated using the Quartus hex editor (word size 32, depth 256). For starters, just using the initialized memory and a simple application to read out the memory contents and printf to the uart. For some reason, only the last 124 addresses appear to provide the correct data and the rest is not instantly recognizable. Here's the code. Can anyone see why this is happening?

Code:

// dp_ram_test.c

#include <stdio.h>

#include <unistd.h>

#include "system.h"

int main()

{

int i=0;

unsigned dp_ram_addr = 0;

unsigned *dp_ram_ptr = 0;

printf("Begin...\n");

printf("Starting at address 0x0000%x\r\n", DP_RAM_BASE);

printf("Hex Addr (dec) : Contents\r\n");

printf("================= : ========\r\n");

for (i = 0; i < 1024; i++)

{

dp_ram_addr = DP_RAM_BASE + i;

dp_ram_ptr = (unsigned *)(dp_ram_addr);

printf("0x0000%x (%u) : %x %u\r\n", dp_ram_addr, dp_ram_addr, *dp_ram_ptr, *dp_ram_ptr);

}

return 0;

}

The hex file (as .pdf) and log file of uart output are attached. Any help would be great. Thanks in advance.

↧

November 25, 2015, 9:51 am

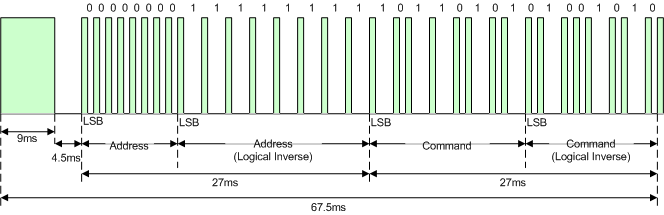

Hi, how can I simulate a NEC Infrared Transmission Protocol precisely in a vector waveform file without doing it manually.

This is the Infrared transmission done manually with the help of time bar. Its long to do and not precise.

![]()

Logical '0' a 562.5µs pulse burst followed by a 562.5µs space, with a total transmit time of 1.125ms

Logical '1' a 562.5µs pulse burst followed by a 1.6875ms space, with a total transmit time of 2.25ms

![]()

Thanks,

Dylan Meng

↧

↧

November 25, 2015, 11:37 am

Hi,

I have got a question about the TK support of the System Console. According to this page:

https://www.altera.com/support/suppo...12014_911.html

I can run a simple GUI with the System Console. The minimal Example on the page works once, so when I run it in my script I get this output:

Code:

% source my_script.tcl

error: invalid command name "???"

while executing

"??? button .b2 -text {World} -underline 0"

(file "my_script.tcl" line 5)

invoked from within

"source my_script.tcl"

Ok there might be something wrong with the text, but that is not the problem at the moment.

When I try to run it again, suddenly something is wrong:

Code:

% source my_script.tcl

error: can't invoke "button" command: application has been destroyed

while executing

"button .b1 -text {Hello} -underline 0"

(file "my_script.tcl" line 3)

invoked from within

"source my_script.tcl"

I would be very happy, if someone could help me with that.

Best Regards,

Philipp

↧

November 25, 2015, 2:36 pm

I'm having trouble building a stopwatch. I'm trying to make it count the secs and mins and have 2 buttons, one for start and pause and one for reset. could anyone help me out? thanks!!!

![]()

↧

November 25, 2015, 8:03 pm

I'm trying to follow this tutorial to generate a preloader for my Terasic DE0-NANO-SOC development board:

http://rocketboards.org/foswiki/view...sLab1Preloader

I'm using the 15.1.0.185 builds of Quartus Prime Lite Edition and SoC EDS Web Edition on a Windows 10 laptop with built-in SD card reader and micro-SD adapter. I keep trying the following step where the final D is my micro-SD drive letter:

Code:

alt-boot-disk-util -p preloader-mkpimage.bin -a write -d D

I always get:

Quote:

device open failed!

The SoC EDS command shell is able to navigate to /cygdrive/d without issue and I can browse the contents of the micro-SD card using Windows explorer. I loaded the DE0-NANO-SOC image described by the tutorial as my starting point. The tutorial uses version 15.0. I tried using components built with 15.1.0.185 and had the same issues as well as a different micro-SD card. Has anyone had success/issues using alt-boot-disk-util with these software/OS versions?

↧

November 26, 2015, 3:04 am

Hi,

I'm trying to create my first HPS system on a C5 Soc board from Terasic.

If I create a system with one JTAG2AVM bridge (called fpga_console in picture qsys_causing_no_error.png) I can run the script shown below, and the leds lit according to the number writen.

Code:

set jtag_master [lindex [get_service_paths master] 0]

open_service master $jtag_master

master_write_8 $jtag_master 0x00010040 1

master_write_8 $jtag_master 0x00010040 2

master_write_8 $jtag_master 0x00010040 3

master_write_8 $jtag_master 0x00010040 4

close_service master $jtag_master

The documentation that I follow from Terasic however tells me that I need to add a second JTAG2AVM Bridge and connect that one up to the f2h_axi_slave (called hps_console in picture qsys_causing_error.png)

When I do this and try to run the script above again, system consoles timesout with an error (see system_console_error_message.png).

I don't understand that this connection, has influence on the fpga_console, that it not connected at all to the HPS or the hps_console.

Any advice?

Is this connection putting the HPS in reset perhaps?

Rgds,

Kimberley

↧

↧

November 26, 2015, 3:08 am

Hi,

I'm conceiving a new Cyclone V E based board implementing a 5CEFA7F23, a DDR, a SRAM and a Flash memory. I wish to configure my FPGA with Asx4 configuration, so I need a QSPI NOR Flash for my board.

Is the EPCQ the only device supported for this type of cofiguration ? Or a QSPI Flash memory from Spansion, like S25FL family, or Micron, like MT25Q/N25Q families, works too ? In fact Altera's EPCQ is quite expensive to be simply a QSPI Flash.

I found these application notes from Spansion and Micron talking about, but only up to Cyclone IV:

https://www.spansion.com/Support/App...I_Flash_AN.pdf

https://www.google.fr/url?sa=t&rct=j...h8UNr1hjE9e2oQ

Thanks.

Ezeri

↧

November 26, 2015, 3:13 am

I need to modify an old project, developed with Quartus II 9.0 on a Stratix III, that contains a DDR2 controlled made using an altmemphy IP. So I installed the software, made the modifications and recomplied it. Unfortunately it is not more possible to generate a working programming file, because with the current Quartus II license file (dated august 2015), the license to compile this IP is not more present. Only a time-limited programming file is generated. So I have the right software, I have a working license, but I cannot use an IP whose license was previously included into the base software. Why?

I configured the license server with the old (expired) license file, and it was possible to compile and generate the programming file, but this cannot be a solution because we have floating licenses running on a server, that is used by many designers.

I tried to run multiple services from the flexlm tool, connected to different IP ports. In this way I could connect to an alternate server port only when I am working on this old project. It works, but after some time, the altera license daemon stops with an error, because it detects another daemon running. I can understand why: if this would be possible, I could easily multiply my licenses, and this is not allowed.

I cannot force the whole company to use an old license (having puchased a new one) file only because I need it... so my question is: is there a "legal" way to do this?

regards

Davide

↧

November 26, 2015, 3:20 am

Hello,

I am using Stratix IV GX dev kit with Quartus v15.0. I would like to run simple socket server example on the design that I created (which is a tweaked version of ethernet standard design example available on altera website). Everything seems to be fine until I get the following errors while building and compiling the simple socket server example in Nios 2 SBT:

Info: Linking simple_socket_server_tse_1.elf

nios2-elf-g++ -T'../simple_socket_server_tse_1_bsp//linker.x' -msys-crt0='../simple_socket_server_tse_1_bsp//obj/HAL/src/crt0.o' -msys-lib=ucosii_bsp -L../simple_socket_server_tse_1_bsp/ -Wl,-Map=simple_socket_server_tse_1.map -O0 -g -Wall -mno-hw-div -mhw-mul -mhw-mulx -o simple_socket_server_tse_1.elf obj/default/alt_error_handler.o obj/default/iniche_init.o obj/default/led.o obj/default/network_utilities.o obj/default/simple_socket_server.o obj/default/tse_my_system.o -lm -msys-lib=m

../simple_socket_server_tse_1_bsp/\libucosii_bsp.a(ins_tse_mac.o): In function `tse_mac_init':

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:267:

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:273: undefined reference to `io_read'

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:283: undefined reference to `io_read'

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:310: undefined reference to `io_write'

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:311: undefined reference to `io_write'

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:315: undefined reference to `io_write'

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:316: undefined reference to `io_write'

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:317: undefined reference to `io_write'

../simple_socket_server_tse_1_bsp/\libucosii_bsp.a(ins_tse_mac.o):E:\tse_tutorial\so ftware\simple_socket_server_tse_1_bsp/drivers/src/iniche/ins_tse_mac.c:318: more undefined references to `io_write' follow

../simple_socket_server_tse_1_bsp/\libucosii_bsp.a(ins_tse_mac.o): In function `tse_mac_init':

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:374: undefined reference to `io_read'

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:385: undefined reference to `io_write'

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:388: undefined reference to `io_read'

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:441: undefined reference to `io_write'

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:442: undefined reference to `io_read'

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:448: undefined reference to `io_write'

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:454: undefined reference to `io_write'

../simple_socket_server_tse_1_bsp/\libucosii_bsp.a(ins_tse_mac.o): In function `tse_mac_raw_send':

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:558: undefined reference to `io_read'

../simple_socket_server_tse_1_bsp/\libucosii_bsp.a(ins_tse_mac.o): In function `tse_mac_rcv':

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:800: undefined reference to `io_write'

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:814: undefined reference to `io_write'

../simple_socket_server_tse_1_bsp/\libucosii_bsp.a(ins_tse_mac.o): In function `tse_mac_close':

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:859: undefined reference to `io_read'

E:\tse_tutorial\software\simple_socket_server_tse_ 1_bsp/drivers/src/iniche/ins_tse_mac.c:860: undefined reference to `io_write'

collect2.exe: error: ld returned 1 exit status

make: *** [simple_socket_server_tse_1.elf] Error 1

I checked that these are all defined in altera_eth_tse_regs.h file (which is included in ins_tse_mac.c). Somehow the compiler is not able to identify them. All these files and functions are default ones. I did not change anything in them.

Can some one help me out here?

Thank you in advance.!

↧

November 26, 2015, 5:31 am

Hello all,

I'm interfacing my DE0-nano with a micro-controller using SPI protocol. The FPGA is acting as a slave and the Micro-controller as a master.

All the input signals of the SPI (MOSI, SCLK, CS) are synchronised with the FPGA clock (100 MHz)

Everything is working fine with low SPI clocks.

Now i'm trying to increase the speed of the SPI(SCLK=5 MHz) but the MISO DATAs are shifted.

With my logic analyzer, I detect the problem. In fact, in the falling edge of the SPI clock , data on the MISO line should be ready before the the next rising edge of SPI clock.But it is not the case.

The time that the MISO data required after the falling edge of the SPI clock is about (0.125 us). So if i want to get high speed communication, i must reduce this delay.

I'd like to ask for help of the experts of community if there is a way to do that.

Kind Regards,

↧

↧

November 26, 2015, 5:40 am

Hi there,

I've got 2 questions related to how to setup my JESD Qsys IP for the TI ADS54J60 ADC.

- Is it correct to fill-in a data rate of 5 Gbps in the Qsys window with the configuration as shown below?

- (1 Gsps * 2 ADCs * 16 bits * (10/8))/ 8 lanes

- Is it correct to calculate the link clock as: 5 Gbps/40 = 125 MHz?

- I don't really understand where this 40 is coming from/based on.

Thank you for your help.

With kind regards,

Patrick

| Sample frequentie |

1 |

Gsps |

Samples per second |

| Data rate |

5 |

Gbps |

Raw data rate per link |

| L |

8 |

# |

Number of lanes per converter device |

| M |

2 |

# |

Number of converters per device |

| F |

2 |

# |

Number of octets per frame |

| S |

4 |

# |

Samples per converter per frame |

| N |

16 |

# |

Number of conversion bits per converter |

| N' |

16 |

# |

Number of transmitted bits per sample |

| K |

32 |

# |

Number of frames per multiframe |

| CS |

0 |

# |

Number of control bits per conversion sample |

| CF |

0 |

# |

Number of control words per frame clock period per link |

| HD |

0 |

# |

High density user data format |

| LMFC |

16 |

Link clock counts |

Local multiframe clock |

↧

November 26, 2015, 11:24 am

Please give me a link for "How to apply time constraint to counter"

Can not find any good explanation.

If counter consist of two or several parts

should i use multicycle for all elements (then 2^32 not acceptable in TimeQuest) or

should i use false_path and

Should I constraint only the the most changing bit or

not.

The counter of 64 bit can be as 4bit and 60 bit, or 4 parts by 16bits, or 2 parts by 32 bits or else.

↧

November 26, 2015, 1:30 pm

hi,

question from total newbie.Plus-sorry for my bad english.

Is it possible to develop applications for old flex 6000 or acex 1k with quartus prime.Or i need to download and install quartus 2 9.0

best regards,

Andjelko.

↧